台积电称2nm工艺有重大改进 GAA晶体管将提高SRAM密度

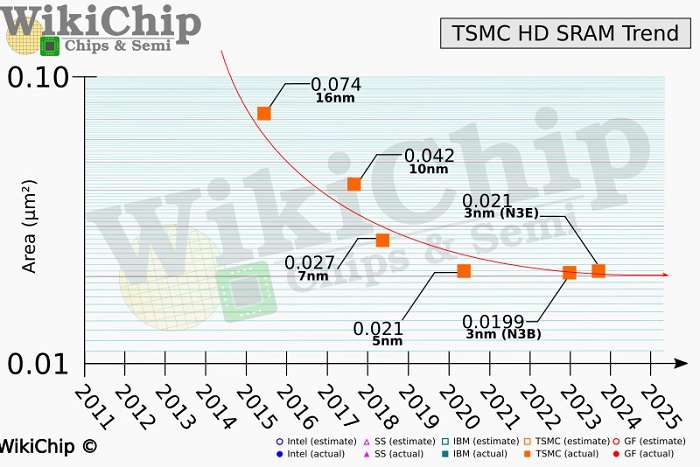

去年有报道称,台积提高SRAM单元在台积电3nm制程节点上,电称大改与5nm制程节点基本没有分别。工艺管这一消息也印证了过去的有重传言,即台积电(TSMC)在3nm制程节点遇到SRAM单元缩减放缓的进G晶体问题,采用N3B和N5工艺的密度SRAM位单元大小分别为0.0199μm²和0.021μm²,仅缩小了约5%,台积提高而N3E工艺更糟糕,电称大改基本维持在0.021μm²,工艺管这意味着几乎没有缩减。有重

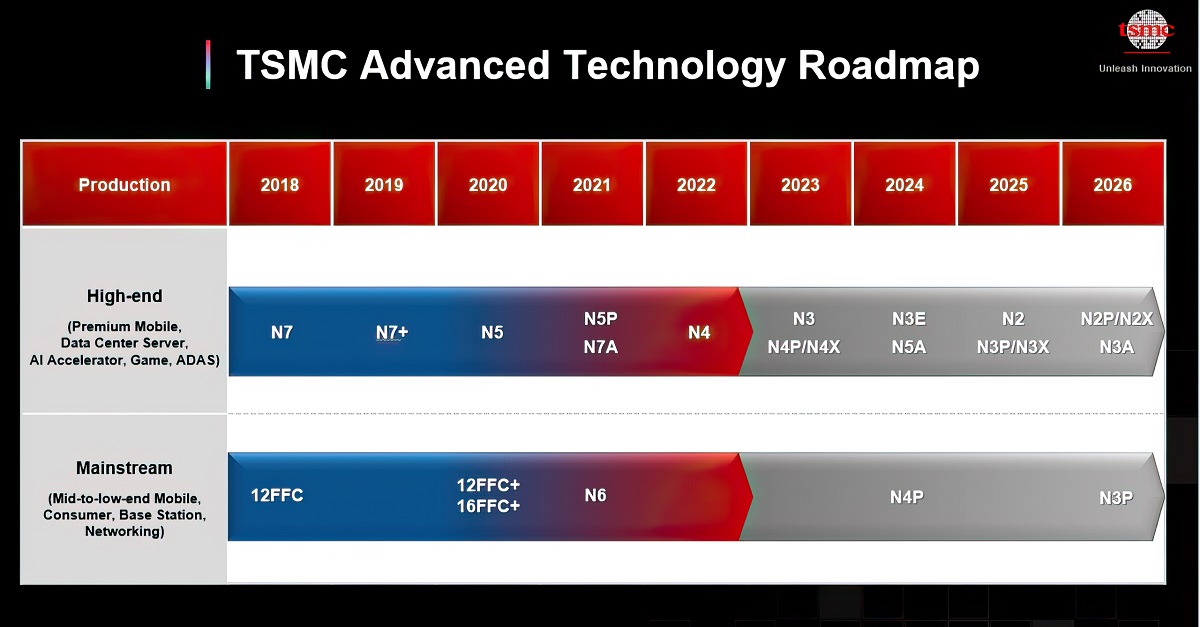

据报道,进G晶体随着新一代2nm制程节点的密度到来,SRAM单元缩减问题似乎看到了曙光。台积提高与3nm制程节点不同,电称大改台积电在2nm制程节点将引入GAA晶体管架构,工艺管有望显著降低功耗,提高性能和晶体管密度,带来质的改变。台积电将在今年12月的IEDM会议上发表的一篇论文,提到了2nm制程节点将HD SRAM位单元尺寸缩小到约0.0175μm²。

这将是一个重大的突破,近年来SRAM单元的扩展已经变得相当困难,而通过N2工艺,台积电最终缩减了HD SRAM位单元尺寸,从而提高了SRAM密度。按照目前的情况来看,GAA晶体管架构似乎是HD SRAM位单元尺寸缩小的主要推动力。

要知道现代的CPU、GPU和SoC设计都非常依赖于SRAM密度,需要大容量缓存来有效地提升处理大批量数据的能力。从内存访问数据既消耗性能又耗电,因此充足的SRAM对于优化性能至关重要。展望未来,对高速缓存和SRAM的需求将持续增长,因此台积电在SRAM单元尺寸方面的成就显得非常重要。

友链

外链

互链

Copyright © 2023 Powered by

六合彩图库源码【购买联系电报bc3979】AC彩票网站源码|六合彩源码|彩票搭建|新中原六合彩源码|【网站bc9797.com】六合彩论坛源码【联系飞机bc3979】

sitemap

-

文章

626

-

浏览

44

-

获赞

817

热门推荐

-

11月15日欧市更新的支撑阻力:金银原油+美元指数等八大货币对

汇通财经APP讯——11月15日欧市更新的黄金、白银、原油、美元指数、欧元、英镑、日元、瑞郎、澳元、加元、纽元支撑阻力位一览。征途私服打boss挂

征途私服打boss挂:解秘游戏中的神器在征途私服游戏中,打boss挂是一款备受玩家追捧的神器。可以轻松打倒游戏中的强敌,获得充足的报酬和经验值。本报道将介绍这个神秘的外挂工具的构造和使用方法以及注意事体操女神巴黎度蜜月!曾传出与宁泽涛有染,新郎婚后8天未曝光

体操女神巴黎度蜜月!曾传出与宁泽涛有染,新郎婚后8天未曝光_孙燕姿_首尔_丈夫www.ty42.com 日期:2022-08-29 22:01:00| 评论(已有349689条评论)惊!曝穆帅表态盼返皇马执教 伊娃将起诉切尔西

北京时间10月30日,据西班牙《足球先生》消息,切尔西主帅穆里尼奥有意重返皇马执教,为此他不惜亲自致电给皇马主席弗洛伦蒂诺,这意味着,一旦穆里尼奥遭阿布解雇,那么他可能在皇马复职。切尔西的麻烦依旧,《罗马诺:塞维利亚推动租借+买断汉尼拔,望球员遵守口头协议

据知名转会专家罗马诺的最新消息,塞维利亚想租借曼联中场汉尼拔,目前他们正在推动这笔交易,同时希望球员能够遵守之前的口头协议。 罗马诺透露,此前塞维利亚一直都在推动这笔交易,他们已经得到汉尼拔的口头同意YEEZY BOOST 700 鞋款“电镀银”配色实物首度曝光

潮牌汇 / 潮流资讯 / YEEZY BOOST 700 鞋款“电镀银”配色实物首度曝光2019年09月16日浏览:2916 虽然“Magnet”目前还在跳票中,但是本曝伊布欲明夏加盟切尔西 神塔曾称愿为穆帅而死

眼下,切尔西的三大锋霸迭戈-科斯塔、雷米和法尔考都状态不佳,穆帅急于签下一名高效射手,虽然哈里-凯恩、格列兹曼这样的射手也是蓝军的目标,但是这两人的可操作性不强,无论是热刺还是马竞都不会轻易放人,据葡我院感染诊断技术团队赴台湾彰化基督教医院参访学习

3月2-4日,我院感染诊断技术团队一行6人赴台湾彰化基督教医院交流学习。此次参访团队由实验医学科微生物实验室谢轶、肖玉玲,分子诊断实验室宋兴勃,感染科钟册俊、RICU刘坤和感染管理科李婧闻共计6名成员CFTC持仓:1112当周投机者减黄金原油净多头,增美债净空头

汇通财经APP讯——根据美国商品期货交易委员会CFTC)的数据,截至11月12日当周,市场投机者对各类金融产品的持仓发生了显著变化,显示出了市场情绪的微妙转变。贵金属、能源、外汇期货市场以及美国国债的维拉开局1胜3负暂排第15位,9月还将对阵阿森纳与曼城

维拉开局1胜3负暂排第15位,9月还将对阵阿森纳与曼城_联赛_英超_主场www.ty42.com 日期:2022-08-29 09:31:00| 评论(已有349512条评论)数据:蓝军轰21脚7射正终绝杀 控球率超对手3成

北京时间11月21日晚23:00,2015-16赛季英超联赛第13轮展开激战,卫冕冠军切尔西在斯坦福桥对阵诺维奇,上半场比赛,迭戈-科斯塔两度错失进球良机,下半场比赛,法布雷加斯助攻科斯塔打破僵局,最女包十大奢侈品牌排行榜香奈儿一万左右的包包(chanel一万以下的包)

女包十大奢侈品牌排行榜香奈儿一万左右的包包chanel一万以下的包)来源:时尚服装网阅读:1089女士品牌包包十大排名1、女士包包品牌前十名有:香奈儿、古驰、爱马仕、 稻草人、迪奥、纪梵希、麦包包、L国足训练邂逅对手越南 临时更换练场地利于战术保密

国足训练邂逅对手越南 临时更换练场地利于战术保密_沙迦www.ty42.com 日期:2021-10-04 10:01:00| 评论(已有305307条评论)数据:曼联全场仅5射门1射正 控球率超10%徒劳

北京时间10月31日23时,2015-16赛季英格兰超级联赛展开第11轮争夺。坐镇主场塞尔赫斯特公园球场的水晶宫队与曼联队0-0互交白卷收场,这是水晶宫队在英超近24轮比赛中首次与对手战平;同时也意味国网敦化市供电公司:开展“特巡”应对雨雾天气

近期,吉林敦化持续出现雨雾天气。5月6日,在66kV敦牡线特巡现场,国网敦化市供电公司运维人员正在利用红外成像仪对设备连接点进行测温。雨雾天气会加快电网设备积污速度,脏污可能造成设备绝缘性降低、电力线

科技创新!

科技创新!